英特爾 以“小芯片”為基,構(gòu)建通用量子計算的軟硬件藍(lán)圖

在量子計算這一前沿科技領(lǐng)域,英特爾正以其深厚的半導(dǎo)體制造與系統(tǒng)集成經(jīng)驗,走出一條獨(dú)特的路徑:從創(chuàng)新的“小芯片”架構(gòu)出發(fā),系統(tǒng)性地布局軟硬件生態(tài),旨在最終實現(xiàn)大規(guī)模、實用化的通用量子計算機(jī)。

硬件基石:“小芯片”與量子比特的融合

英特爾的核心硬件策略,是將其在經(jīng)典計算中成熟的“小芯片”設(shè)計與封裝技術(shù),遷移并適配到量子芯片的開發(fā)中。傳統(tǒng)上,量子處理器依賴于單一、復(fù)雜的單片集成,制造難度和良率是巨大挑戰(zhàn)。英特爾的思路是,將量子比特的控制電路、互連乃至部分經(jīng)典協(xié)處理單元,以模塊化的“小芯片”形式分別制造和優(yōu)化,再通過先進(jìn)封裝技術(shù)(如英特爾EMIB或Foveros)進(jìn)行高密度、高性能的集成。

這種“小芯片”模式帶來多重優(yōu)勢:

- 可擴(kuò)展性:如同搭積木,可以通過增加“小芯片”模塊來堆疊量子比特數(shù)量,為通向百萬比特級大規(guī)模集成鋪平道路。

- 制造靈活性:不同功能的芯片可采用最適合的工藝節(jié)點制造,例如用成熟制程做控制電路,用前沿工藝探索新型量子比特,提升整體效率和良率。

- 性能優(yōu)化:將控制電子器件盡可能靠近量子比特,能減少信號延遲和噪聲,這是提升量子比特保真度的關(guān)鍵。

目前,英特爾正重點推進(jìn)其硅自旋量子比特技術(shù)。這種量子比特基于與現(xiàn)有CMOS工藝兼容的硅材料,有望利用龐大的半導(dǎo)體制造基礎(chǔ)設(shè)施進(jìn)行規(guī)模化生產(chǎn),與“小芯片”理念高度契合。

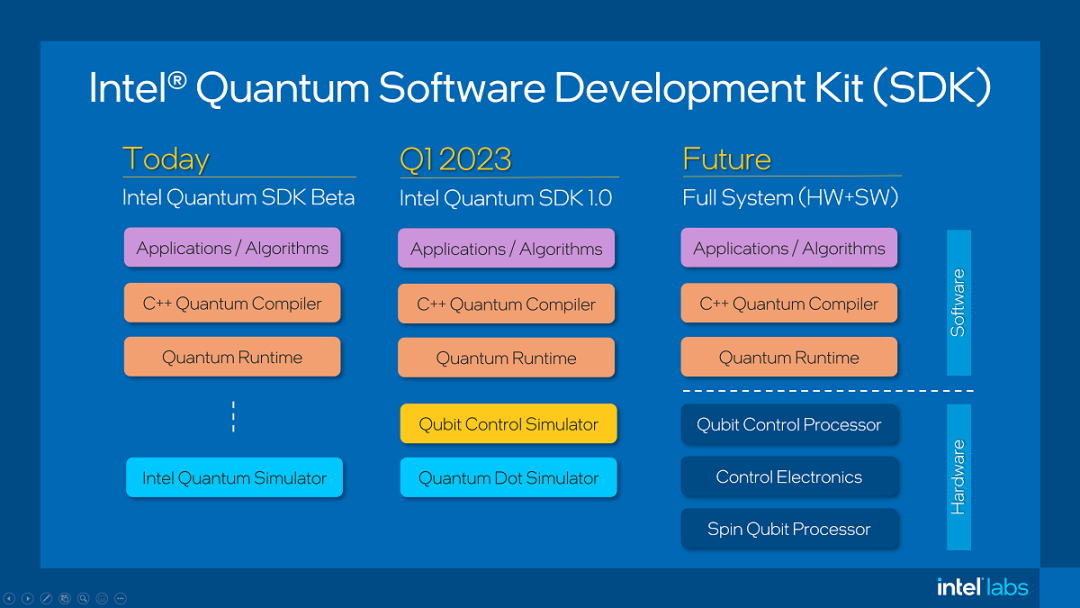

軟件橋梁:連接量子硬件與應(yīng)用

僅有強(qiáng)大的硬件遠(yuǎn)遠(yuǎn)不夠。英特爾深知,要讓量子計算機(jī)解決實際問題,必須構(gòu)建強(qiáng)大的軟件棧來“駕馭”硬件。其軟件戰(zhàn)略是打造一個從底層控制到上層應(yīng)用的完整工具鏈:

- 底層控制與編譯器:開發(fā)高效的量子位控制軟件和編譯器,能將高級量子算法“翻譯”成硬件可執(zhí)行的基本操作序列。英特爾的研究重點之一是優(yōu)化控制脈沖,以最大限度降低錯誤率。

- 中間件與模擬器:提供強(qiáng)大的量子計算模擬環(huán)境,讓開發(fā)者在獲得真實硬件前就能測試和調(diào)試算法。這對于算法研究和教育至關(guān)重要。

- 應(yīng)用與算法庫:與行業(yè)伙伴合作,針對化學(xué)模擬、材料科學(xué)、物流優(yōu)化等特定領(lǐng)域,開發(fā)實用的量子算法和應(yīng)用案例,展示量子加速的實際價值。

系統(tǒng)集成:走向通用的關(guān)鍵

英特爾的終極目標(biāo)是構(gòu)建通用量子計算機(jī)。這要求將前述的量子“小芯片”、低溫控制、錯誤校正、經(jīng)典協(xié)處理器以及軟件棧,集成為一個穩(wěn)定運(yùn)行的系統(tǒng)。其中,錯誤校正是核心挑戰(zhàn)。英特爾正在研究如何將其在系統(tǒng)架構(gòu)和容錯計算方面的專長,應(yīng)用于構(gòu)建高效的量子糾錯方案,這是實現(xiàn)長時、可靠量子計算的基礎(chǔ)。

###

英特爾在量子計算上的布局,體現(xiàn)了一種務(wù)實的系統(tǒng)工程思維:不追求單一的量子比特數(shù)量突破,而是著眼于整個計算棧的協(xié)同創(chuàng)新與可擴(kuò)展性。通過“小芯片”架構(gòu)降低硬件復(fù)雜度與制造成本,通過全棧軟件生態(tài)釋放硬件潛力,最終通過系統(tǒng)集成邁向通用量子計算。這條路徑或許并非最快,但可能是最穩(wěn)健、最具規(guī)模化潛力的道路之一,有望在未來十年內(nèi),將量子計算從實驗室原型推向?qū)嶋H應(yīng)用。

如若轉(zhuǎn)載,請注明出處:http://www.lhjpjq.cn/product/47.html

更新時間:2026-01-07 05:15:26